::: reklama@pbprog.kz

::: editor@pbprog.kz

::: webmaster@pbprog.kz

TSMC разрабатывает гигантскую версию технологии CoWoS

TSMC разрабатывает версию своей технологии CoWoS, которая позволит партнёрам создавать многочиповые сборки размером 9,5-сетка (7885 мм^2) на подложках 120×150 мм (18000 мм^2), что немного больше размера корпуса компакт-диска. TSMC утверждает, что эти гиганты могут быть в 40 раз производительнее стандартного процессора.

Практически все современные высокопроизводительные процессоры для центров обработки данных используют многокристальные конструкции, и по мере роста требований к производительности разработчики хотят интегрировать в свои продукты ещё больше кремния.

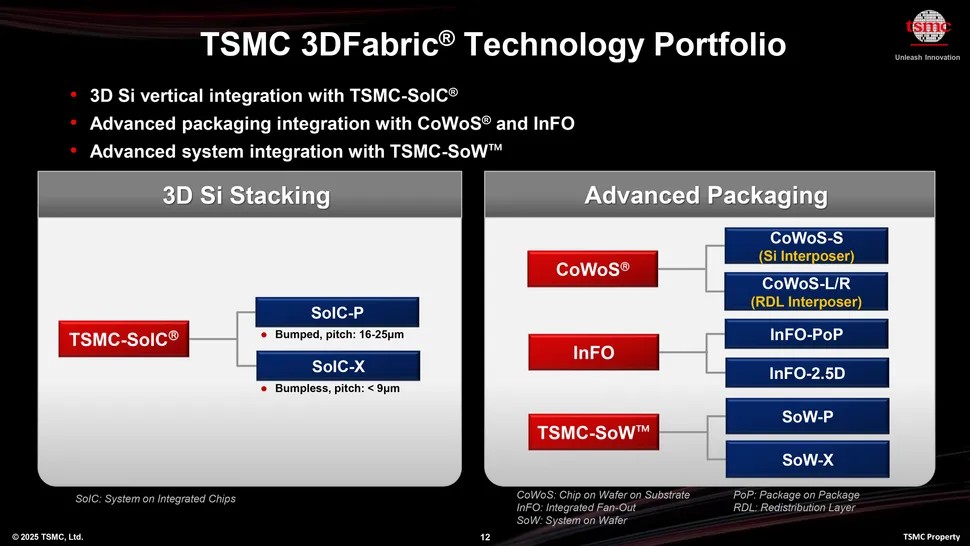

Стремясь удовлетворить спрос, TSMC расширяет свои возможности по упаковке, чтобы поддерживать значительно более крупные микросхемы для высокопроизводительных вычислений и приложений искусственного интеллекта. На Североамериканском технологическом симпозиуме TSMC представила свою новую дорожную карту 3DFabric, которая направлена на масштабирование размеров межсоединений далеко за пределы текущих ограничений.

От большого к огромному

В настоящее время TSMC CoWoS предлагает решения для упаковки микросхем, которые позволяют использовать межсоединения площадью до 2831 мм^2, что примерно в 3,3 раза больше, чем максимальный размер решётки (фотошаблона) компании (858 мм^2 по стандарту EUV, TSMC использует 830 мм^2). Эта возможность уже используется в таких продуктах, как ускорители AMD Instinct MI300X и графические процессоры Nvidia B200, которые сочетают в себе два больших логических чипа для вычислений с восемью стеками памяти HBM3 или HBM3E. Но этого недостаточно для будущих приложений.

Возможно, в следующем году или чуть позже TSMC планирует представить следующее поколение своей технологии упаковки CoWoS-L, которая будет поддерживать межсоединения площадью до 4719 мм^2, что примерно в 5,5 раз больше стандартной площади решётки. В упаковке можно будет разместить до 12 стеков памяти с высокой пропускной способностью, и для неё потребуется подложка большего размера — 100×100 мм (10 000 мм^2). Компания ожидает, что решения, построенные на базе этого поколения упаковки, будут более чем в три с половиной раза производительнее существующих разработок. Хотя этого решения может быть достаточно для графических процессоров Nvidia Rubin с 12 стеками HBM4, процессорам, которые будут предлагать более высокую вычислительную мощность, потребуется ещё больше кремния.

Заглядывая в будущее, TSMC намерена ещё больше масштабировать этот подход к упаковке. Компания планирует предложить разделители площадью до 7885 мм^2, что примерно в 9,5 раз превышает предел фотошаблона, на подложке размером 120×150 мм (для сравнения, стандартный футляр для компакт-диска имеет размеры примерно 142×125 мм).

Это больше, чем 8-кратная сборка из нескольких чипов на подложке размером 120×120 мм, которую TSMC представила в прошлом году, и это увеличение, вероятно, отражает запросы клиентов литейного завода. Ожидается, что такой корпус будет поддерживать четыре 3D-слоя систем на интегральных схемах (SoIC, например, кристалл N2/A16, установленный поверх логического кристалла N3), двенадцать слоёв памяти HBM4 и дополнительные кристаллы ввода-вывода (I/O Die).

Однако у TSMC есть клиенты, которым нужна максимальная производительность, и они готовы за неё платить. Для них TSMC предлагает технологию System-on-Wafer (SoW-X), которая обеспечивает интеграцию на уровне пластины. На данный момент только Cerebras и Tesla используют интеграцию на уровне пластины для своих процессоров WFE и Dojo для ИИ, но TSMC считает, что помимо этих двух компаний найдутся и другие клиенты с аналогичными требованиями.

Подача энергии

Без сомнения, процессоры размером с 9,5-дюймовую матрицу или с размером пластины сложно создавать и собирать. Но для таких решений с несколькими чипами требуется подача питания мощностью в киловольт, и производителям серверов и разработчикам чипов становится всё сложнее это делать, поэтому эту проблему необходимо решать на системном уровне. На технологическом симпозиуме 2025 года компания TSMC представила стратегию подачи питания, разработанную для обеспечения эффективной и масштабируемой подачи питания мощностью в киловольт.

Чтобы обеспечить питанием процессоры с энергопотреблением в киловаттном диапазоне, TSMC хочет интегрировать монолитные микросхемы управления питанием (PMIC) с TSV, изготовленными по технологии TSMC N16 FinFET, и индукторами на пластине непосредственно в корпуса CoWoS-L с промежуточными элементами RDL, что позволит направлять питание через саму подложку. Это сокращает расстояние между источниками питания и активными кристаллами, снижая паразитное сопротивление и повышая целостность питания всей системы.

TSMC утверждает, что её PMIC на базе N16 может легко справляться с точным контролем напряжения для динамического масштабирования напряжения (DVS) при требуемых уровнях тока, обеспечивая в пять раз более высокую плотность мощности по сравнению с традиционными подходами. Кроме того, встроенные в межслойную пластину или кремниевую подложку конденсаторы с глубокой канавкой (eDTC/DTC) обеспечивают развязку высокой плотности (до 2500 нФ/мм^2) для повышения стабильности питания за счёт фильтрации колебаний напряжения вблизи кристалла и обеспечивают надёжную работу даже при быстрой смене рабочей нагрузки. Такой встроенный подход обеспечивает эффективное управление энергопотреблением и улучшенную переходную характеристику, что крайне важно для управления энергоэффективностью в сложных многоядерных или многокристальных системах.

Форм-фактор и охлаждение

Переход на подложки гораздо большего размера повлияет на проектирование систем, особенно с точки зрения форм-факторов корпусов. Планируемая подложка размером 100×100 мм близка к физическим ограничениям форм-фактора OAM 2.0, который имеет размеры 102×165 мм. Последующая подложка размером 120×150 мм будет превышать эти размеры, что, вероятно, потребует новых стандартов для корпусов модулей и компоновки плат, чтобы учесть увеличенный размер.

Помимо физических ограничений и энергопотребления, эти огромные многочиплетные фильтры выделяют огромное количество тепла. Для решения этой проблемы производители оборудования уже изучают передовые методы охлаждения, включая прямое жидкостное охлаждение (технология, уже применяемая Nvidia для своих моделей GB200 / GB300 NVL72) и технологии иммерсионного охлаждения, позволяющие выдерживать тепловые нагрузки, связанные с многокиловаттными процессорами. Однако TSMC не может решить эту проблему на уровне чипа или SiP — по крайней мере, на данный момент.